FIFO IP核的使用教程

引言

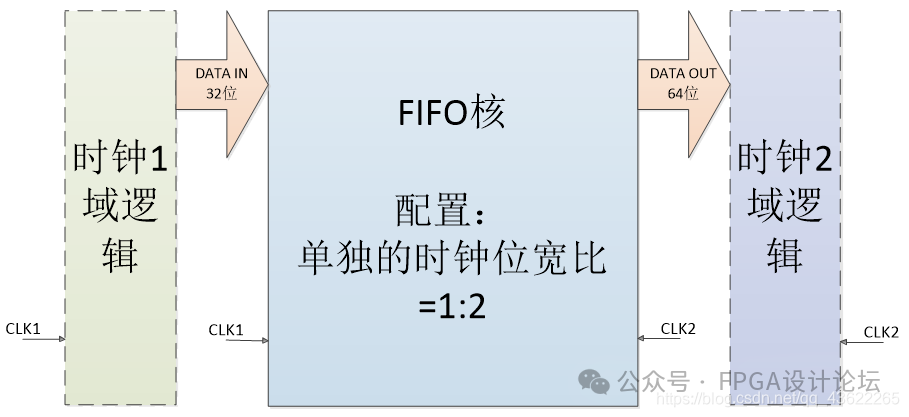

在数字设计中,利用FIFO进行数据处理是非常普遍的应用,例如,实现时钟域交叉、低延时存储器缓存、总线位宽调整等。下图给出了FIFO生成器支持的一种可能配置。

设计中有两个独立的时钟域并且读数据总线的位宽是写数据总线位宽的2倍。使用FIFO生成器可以快速实现这种配置,从而在Xilinx FPGA芯片上实现特定的设计要求。

实际应用案例:本案例背景是将信号处理系统中ADC采集到的数据写入FPGA芯片外挂的DDR3,完成采样数据的存储。ADC采样率设定为96Mhz,两个采样点(两个16bit数据拼接成一个32bit)为单位,DDR读写时钟速率为150Mhz,总线数据位宽64