Quartus Prime Pro 25.1版本的安装和使用

如果用户开发板是基于Agilex 3、Agilex 5等高阶器件,则需要安装高版本的Quartus软件比如Quartus Prime Pro 25.1版本,这个版本在安装包和license获取(免费)等方面跟以往的Quartus软件略有不同,本文将一步步演示该版本的软件安装、工程创建和仿真验证。

一 安装Quartus 软件

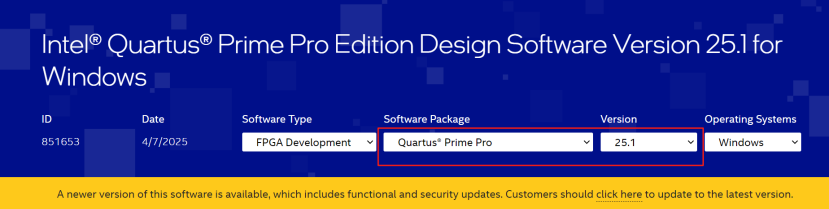

进入Altera官网选择Quartus Prime Pro 25.1版本:

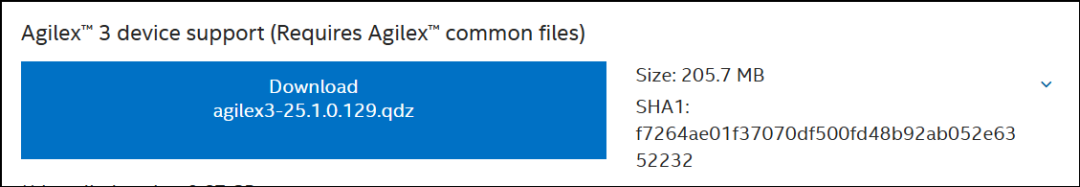

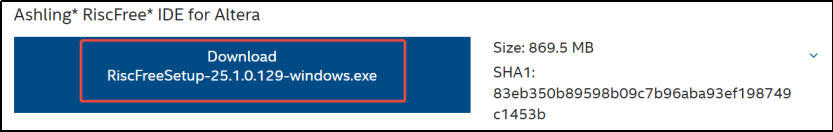

然后点击Inpidual Files,选择Quartus Prime Pro Edition Part 1&Part2、 Ashling RiscFree IDE Altera(如果创建Nios V 工程则需要该文件包) 、 QuestaSetup-25.1.0.129-windows.exe、Agilex 3 器件支持包(如果是Agilex5的板子则下载Agilex 5 器件支持包)、Agilex common 文件共6个文件并下载:

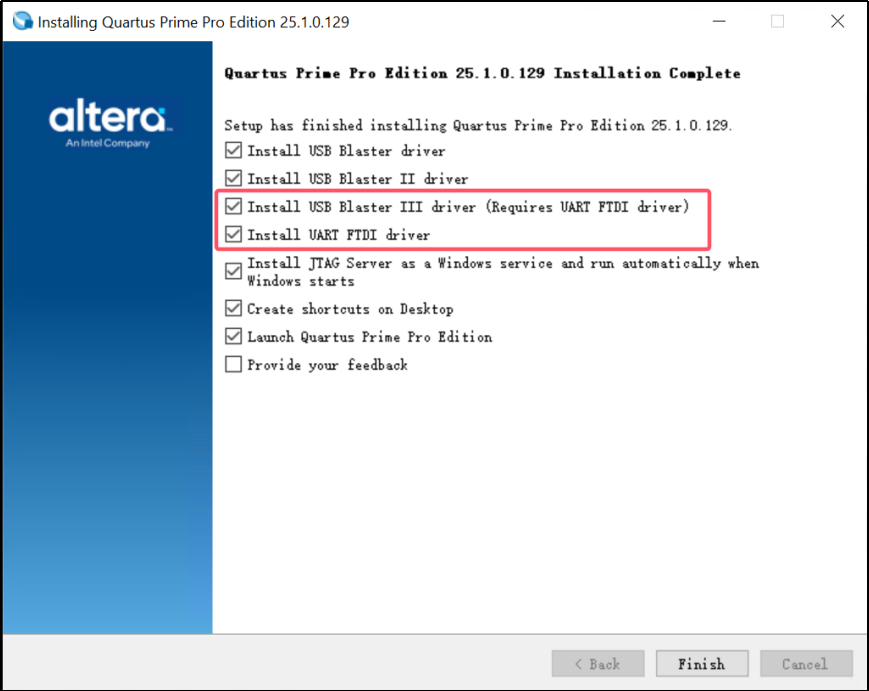

所有文件都下载完以后,双击QuartusProSetup-25.1.0.129-windows.exe文件进行安装。安装的过程中会默认选择一起安装Ashling RiscFree IDE和Agilex3器件包以及Questa等,建议安装的过程中所有默认设置都保留(除了安装路径自己选择外)。USB Blaster III驱动程序将在软件安装结束时安装如下图所示:

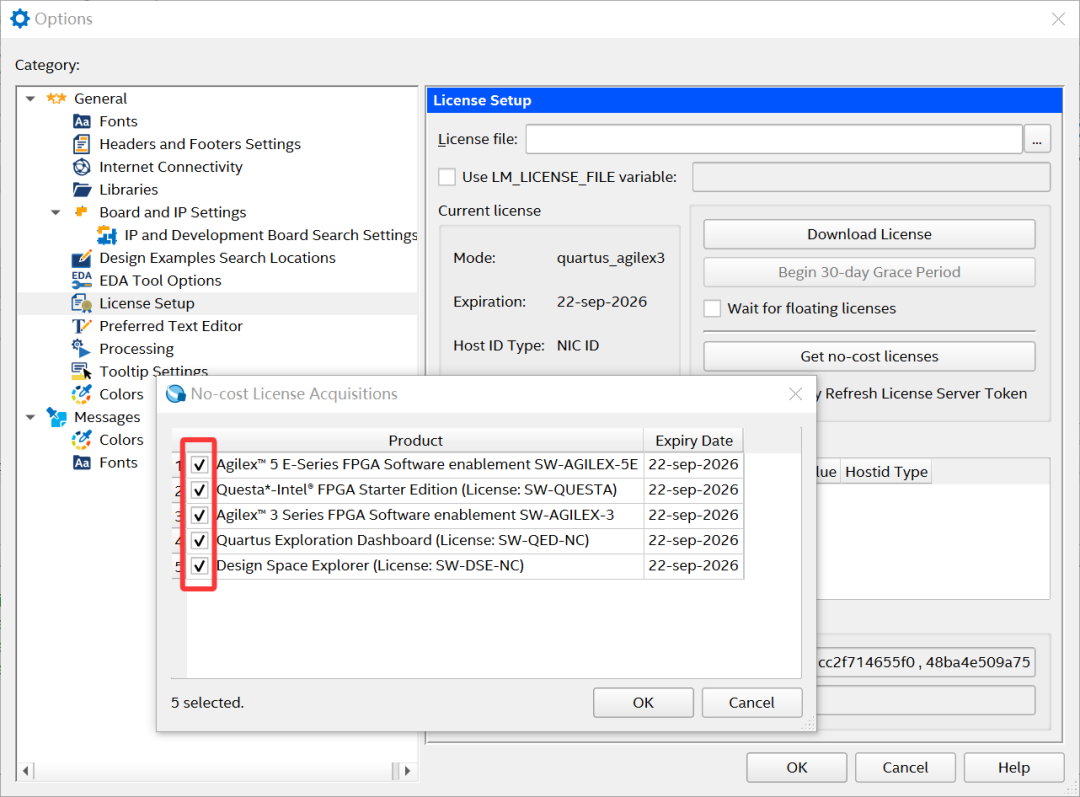

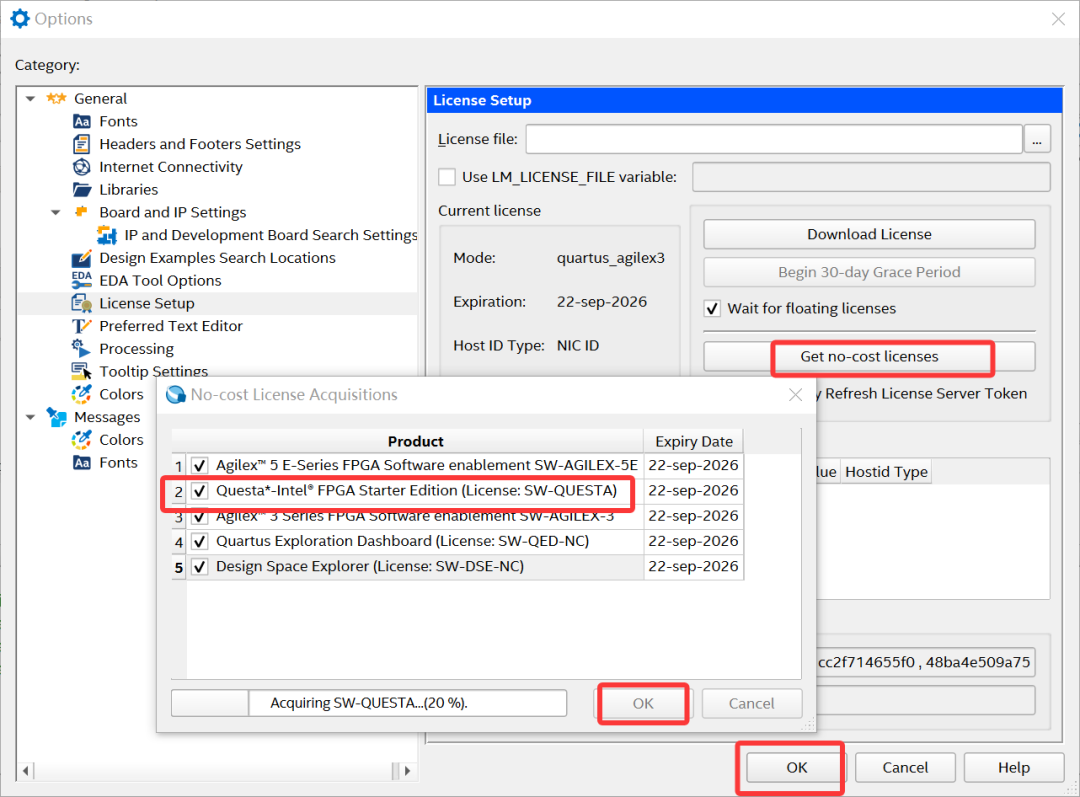

重要提示:Altera Agilex 5、Agilex 3的开发人员能够免费访问Intel Quartus Pro Edition软件-无需额外购买许可证,从而充分利用Quartus Pro的设计和编译功能。有关如何获得免费许可证的详细信息,请参阅英特尔的官方指南:Acquiring Free No-Cost Licenses for Intel Agilex 5 Devices或者直接参考以下步骤:双击电脑桌面Quartus Prime Pro 25.1 的图标打开Quartus, 点击菜单Tools——License Setup, 然后点击 Get no-cost licenses, 将如下复选框全部选上:

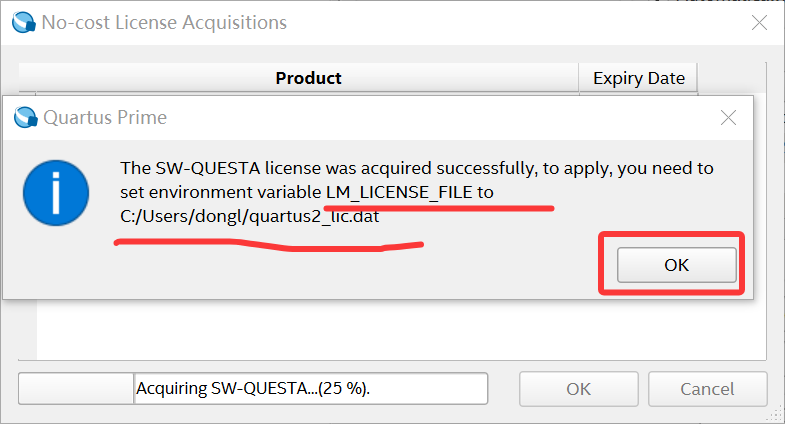

这时会提示仿真器Questa的license文件位置,并提醒用户去设置环境变量:

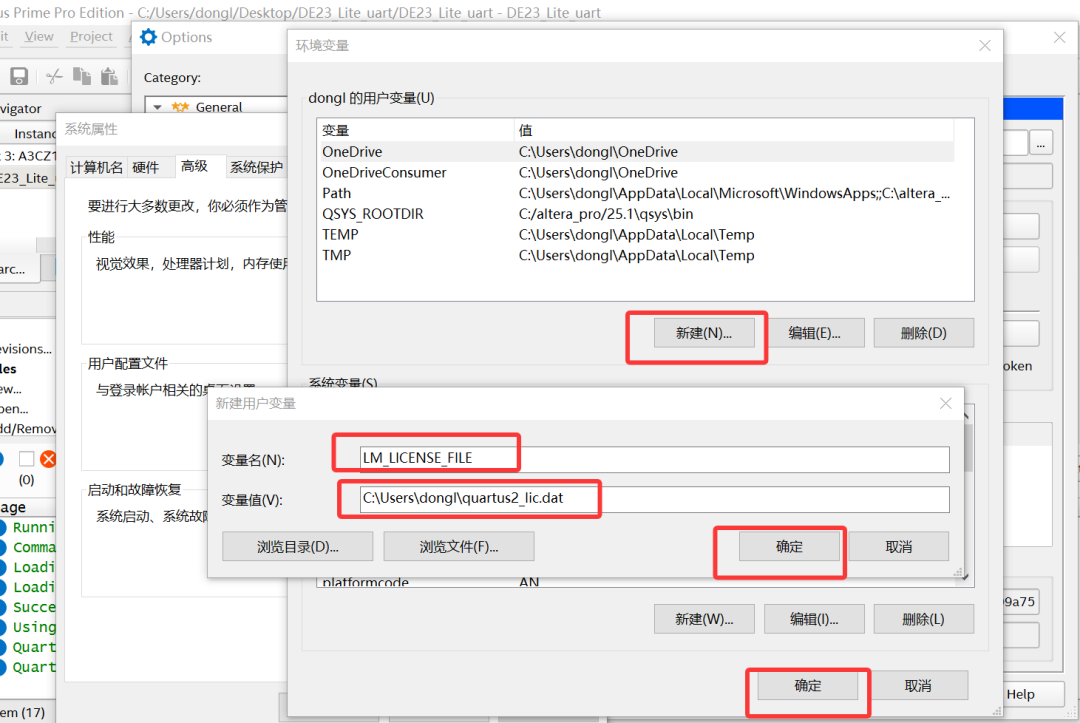

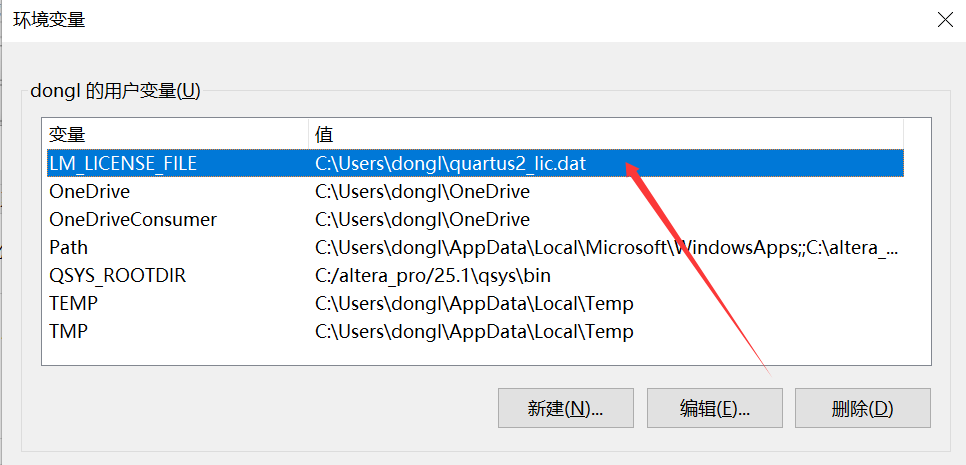

打开电脑的环境变量设置窗口,如点击 系统信息——高级系统设置——环境变量——新建,变量名填入LM_LICENSE_FILE, 变量值填入Questa license文件quartus2_lic.dat的路径:

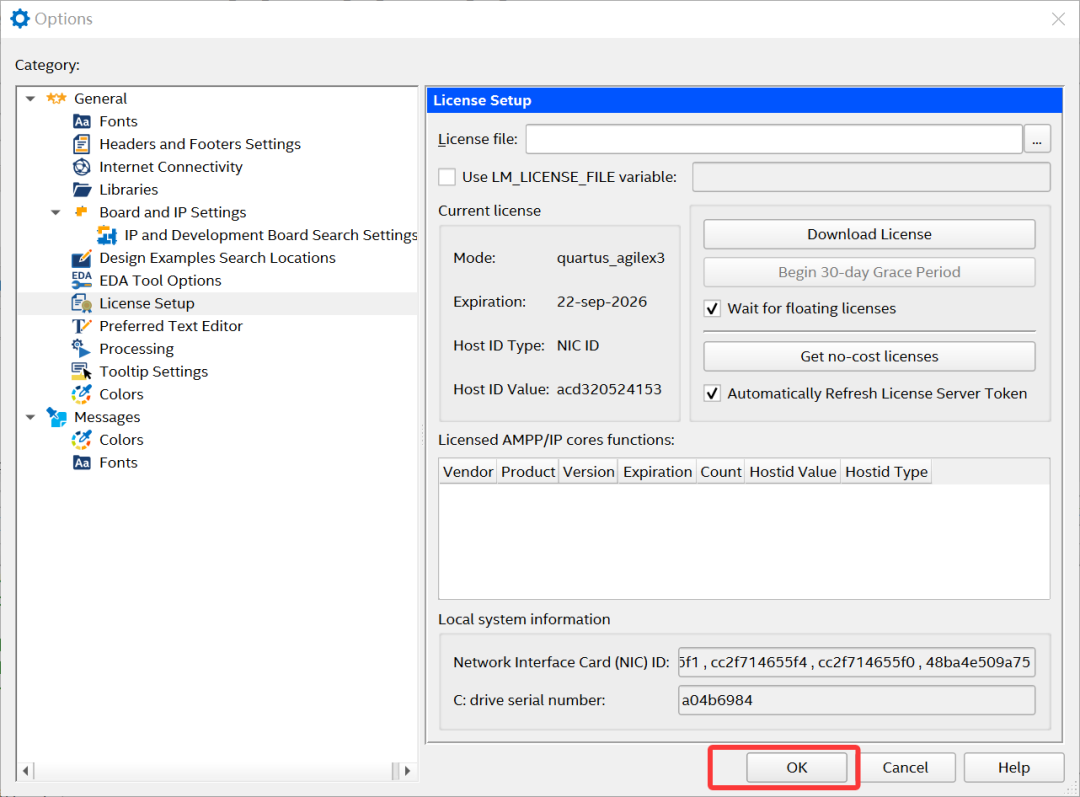

返回到Quartus软件界面,最后点击OK关闭掉该License Setup窗口。

二 创建工程

本文将演示一个简单全加器的工程设计。

1. 双击桌面的Quartus图标打开Quartus工具。

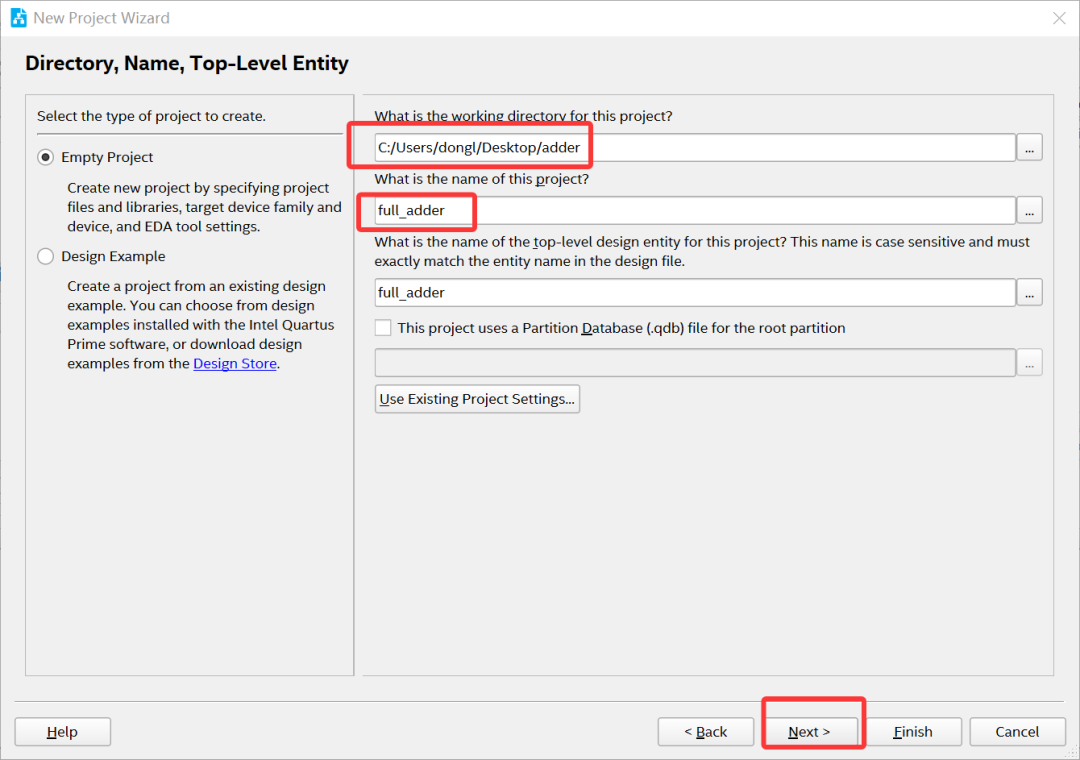

2. 点击File——New Project Wizard...——Next,然后指定工程路径,编辑工程名称。

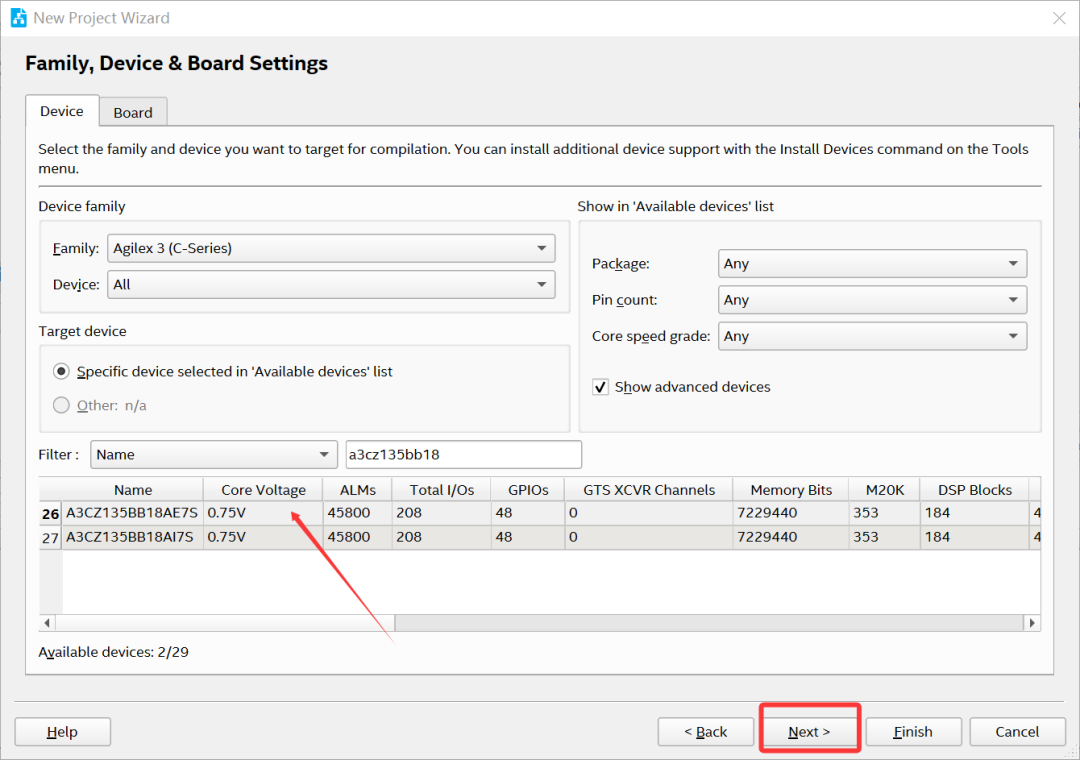

3. 点击Next,器件选择A3CZ135BB18AE7S(这个器件正好是DE23-Lite开发板上对应的FPGA device):

4. 继续点击Next,然后点击Finish关闭窗口。

5. 点击File——New,选择Verilog HDL File,点击OK来创建top文件。将如下代码拷贝到新建的文件,并保存为full_adder.v:

module full_adder( inputa, inputb, inputcin, outputsum, output cout ); assignsum= a ^ b ^ cin; //将a、b、cin进行与或运算,赋值给sum assign cout= (a & b) | ((a^b) & cin); //将a、b、cin进行组合逻辑运算,赋值给cout endmodule

6. 点击File——New,选择Verilog HDL File,点击OK来创建tb文件。将如下代码拷贝到新建的文件,并保存为full_adder_tb.v:

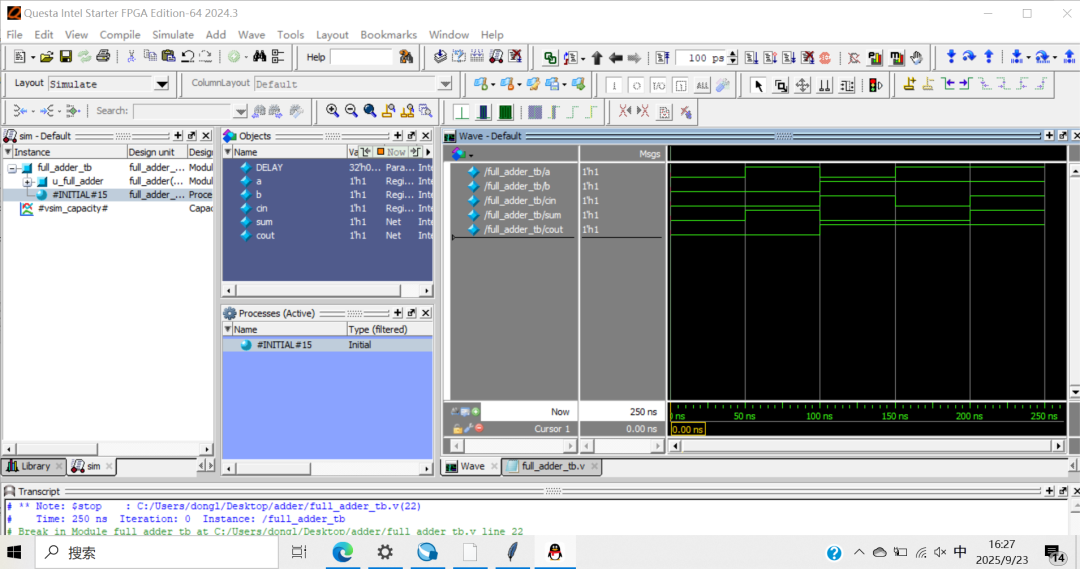

`timescale1ns /1ns //设定时间单位和时间精度,时延单位为1ns,时延精度为1ns module full_adder_tb; //待测试的加法器模块 reg a,b,cin; //数据输入 wire sum,cout; //输出信号 parameter DELAY=50; //设置延迟参数为50 full_adderu_full_adder( //例化被测试模块 a, b, cin, sum, cout ); initial //使用initial过程快定义激励信号波形 begin //使用begin-end控制语句 a =1'b0; b = 1'b0; cin =1'b0; //初始化输入,被加数a被赋值为0,加数b被赋值为0,进位输入c被赋值为0,此时加和sum和进位输出cout都应该为0 #DELAYa = 1'b1; b =1'b0; cin = 1'b0;//在50ns时,被加数a被赋值为1,加数b被赋值为0,进位输入c被赋值为0,此时加和sum应该为1,进位输出cout应该为0 #DELAY a = 1'b0; b = 1'b1; cin = 1'b1; //在100ns时,被加数a被赋值为0,加数b被赋值为1,进位输入c被赋值为1,此时加和sum应该为0,进位输出cout应该为1 #DELAY a = 1'b1; b = 1'b1; cin = 1'b0; //在150ns时,被加数a被赋值为1,加数b被赋值为1,进位输入c被赋值为0,此时加和sum应该为0,进位输出cout应该为1 #DELAY a = 1'b1; b = 1'b1; cin = 1'b1; //在200ns时,被加数a被赋值为1,加数b被赋值为1,进位输入c被赋值为1,此时加和sum应该为1,进位输出cout应该为1 #DELAY $stop; //在250ns时,执行$stop系统任务,停止仿真 end initial $monitor($time,,,"a=%b,b=%b,cin=%b,sum=%b,cout=%b",a,b,cin,sum,cout);//执行monitor系统任务,设置显示结果的格式 endmodule

三 Questa 仿真

首先确保Questa 的license已经获取(参考第一部分license获取内容):

并且环境变量已经设置好了(参考第一部分license获取内容):

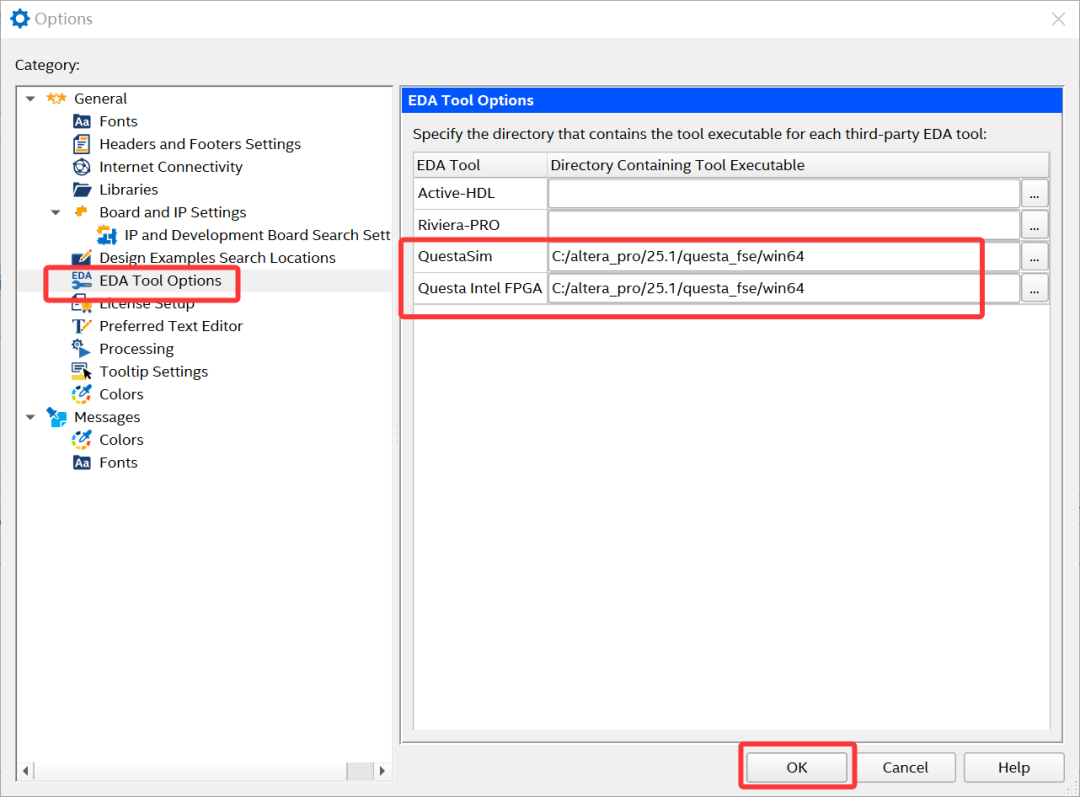

打开Quartus Tools-->Options,在EDA Tool Options里设置Questa工具路径,如下图所示。

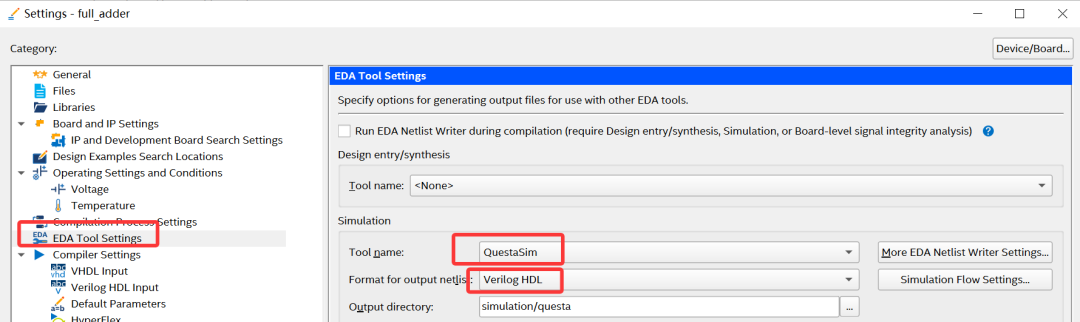

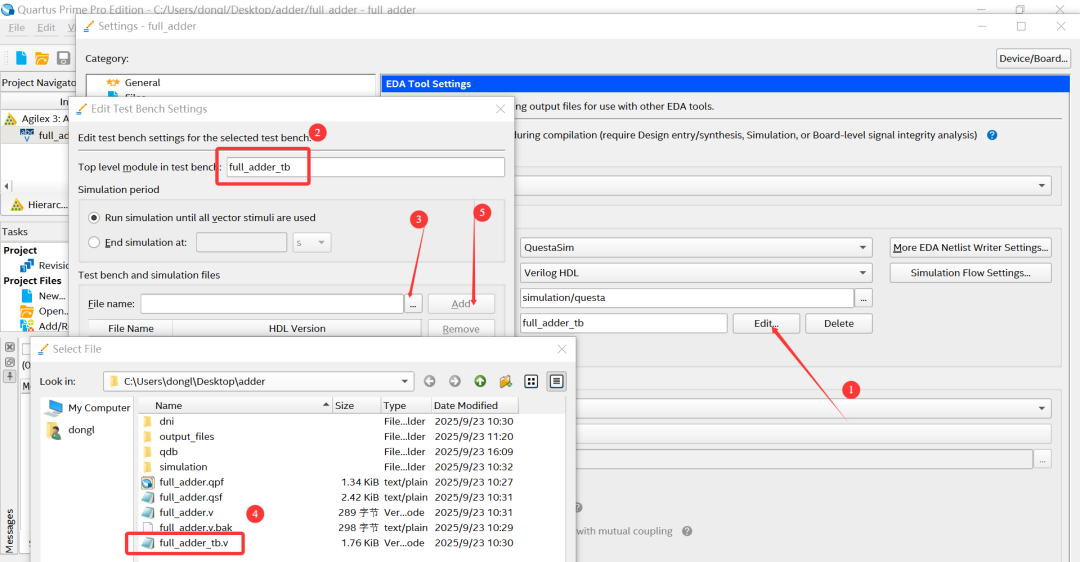

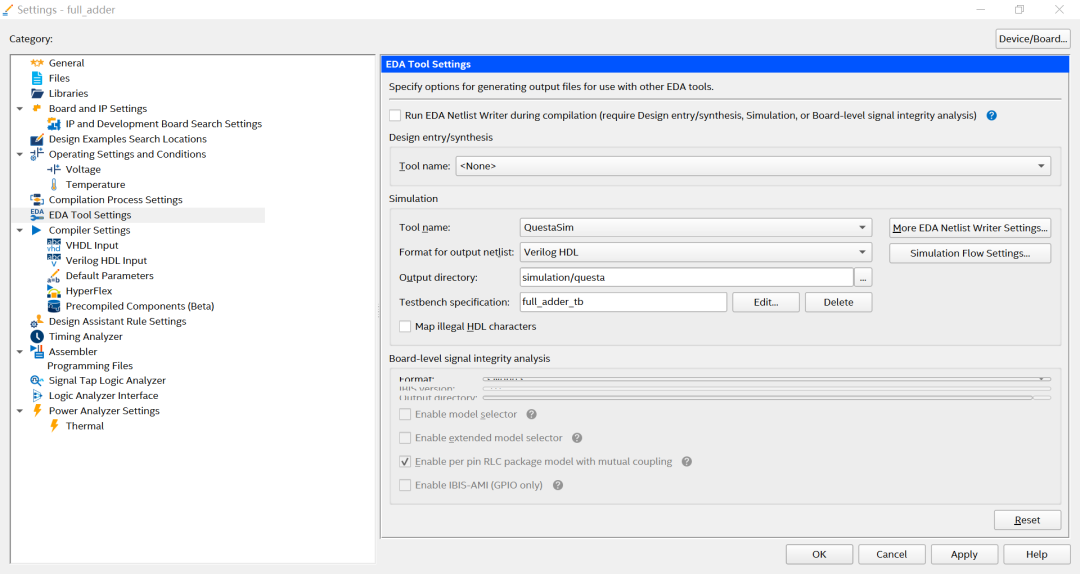

点击Assignment——Settings...——EDA Tool Settings去指定仿真工具,指定仿真文件:

最后点击Apply 和OK关闭当前窗口:

设置好后点击Quartus Tools-->Run Simulation Tool-->RTL Simulation即可运行仿真(这个过程会自动对工程进行分析和综合的操作)。

注: 若在运行RTL Simulation时没有Questa 软件出现,可能是license文件的环境变量没有设置,或者是设置了环境变量但没有重启Quartus软件让变量生效。

- Quartus Prime Pro 25.1版本的安装和使用

- 串口以太网模块与三菱以太网通信处理器的 FX3U PLC - 触摸屏通讯应用案例

- 图扑数字孪生静态交通一网统管 | 智慧停车场合集

- 【有资料】开源CW32L011电机驱动器,硬件支持FOC

- ZWS云平台:储能经销商和终端业主的智能助手

- 倾佳电子代理的基本半导体驱动IC及电源IC产品力深度解析报告

- 东芝亮相2025上海国际电力元件和可再生能源管理展览会

- 推拉力测试机测试模块选择,看完选择不迷茫

- 加氢站和电力系统,谁是AEM产业化破局的关键?

- 翼辉软PLC方案的技术创新与实践

- AI安防选什么主板?杰和IB3-761靠“算力精准+多接口”出圈

- 信捷XS STUDIO编程软件V2.3.2版本的全新功能

- 诚迈科技与理想汽车签署合作备忘录,携手共建理想星环OS开源生态

- 光通信测试领域的精准利器:Agilent N7768A 多端口光开关解析

- 中国最大传感器公司,进入英伟达供应链!

- 金升阳LD20-26BxxR2系列AC/DC电源产品优势